Patent News: Perfect detection of concurrent faults ..

Perfect detection of concurrent faults in CMOS circuits by exploiting reversible and preservative Gates

Patent Details: Altun, Mustafa, and Sajjad Parvin. "Perfect detection of concurrent faults in CMOS circuits by exploiting reversible and preservative gates." U.S. Patent No. 11,307,252. 19 Apr. 2022.

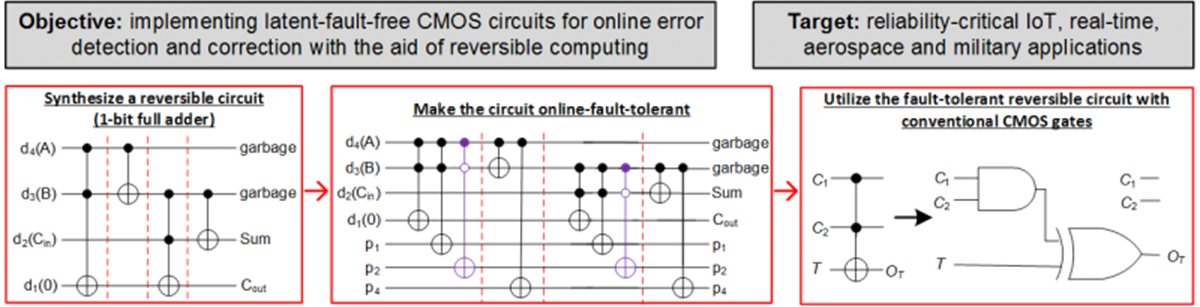

Brief description: Unlike conventional CMOS circuits, reversible circuits do not have latent faults, so faults occurring in internal circuit nodes always result in an error at the output. This is a unique feature for online or concurrent fault tolerance. Motivated by this, we implement error tolerant CMOS circuit blocks by exploiting reversible computing. We first synthesize reversible circuits with reversible gates; then we make them fault-tolerant; and finally we perform conversion from reversible gates to CMOS gates.

Perfect Online Error Detection

In order to achieve a CMOS circuit having 100% online or concurrent error detection, we exploit reversible computing by proposing a new, fault preservative, and reversible gate library. We ensure that the parity, even or odd, is preserved at all levels including the output level unless there is a faulty node.

Online Error Detection and Correction

We develop two techniques to make a reversible circuit fault-tolerant by using multiple-control Toffoli gates. The first technique is based on single parity preserving, and offers error detection for odd number of errors at the output. The second technique is constructed on Hamming codes for error correction. We also claim that perfect error detection is possible with conservative reversible gates such as a Fredkin gate. As the next step, we utilize the proposed reversible circuits with conventional CMOS gates.

Google Patent PDF Link